- 2017/5/18 10:26:58

- 类型:原创

- 来源:电脑报

- 报纸编辑:胡进

- 作者:

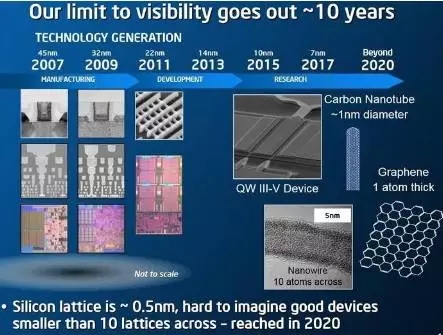

以前一扯到CPU关于新制程进程方面的东西,一些大佬就要开始提摩尔定律,作为Intel创始人之一戈登·摩尔提出的这项理论,intel无疑是目前最为坚定的捍卫者之一,不过随着现目前台积电和三星方面在工艺节点方面的全面超越已经开始量产10nm和即将试产的7nm工艺,在进度方面那可是比Intel方面快多了,很多朋友到现在也没有想清楚具体原因,今儿个小狮子就来跟大家聊这个话题(没错!“永恒之蓝”病毒问题因为素材太多又跳票一期(⊙v⊙)

我记得..Intel不一直是大佬吗?

道理是这样的没错,不过现目前基于智能手机的工艺发展趋势,整体上两家半导体公司在工艺节点上对Intel进行了全面超越,大佬自然是坐不住的;甚至专门给出了统一衡量工艺标准的相关公式,也借此希望友商能够稍微“诚实”一些。

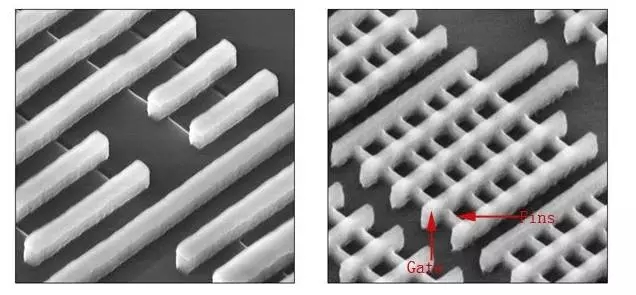

让大家调侃两句大佬就坐不住了?肯定是没有那么简单的,小狮子就先来说说为什么Intel要介意这个问题,我们就说早在几年前的时候,当时Intel在半导体方面1000%是要领先于台积电的,更别说那个时期的三星半导体,因为当年在22nm节点的时候Intel就已经率先量产我们现在经常能看到的3D FinFET工艺,而那个时候三星和台积电实际上才刚刚开始推出自家的28nm工艺还没有多久,所以无论从封装工艺还是制程节点方面都是处于全面的落后状态的。

转折点,就在这里

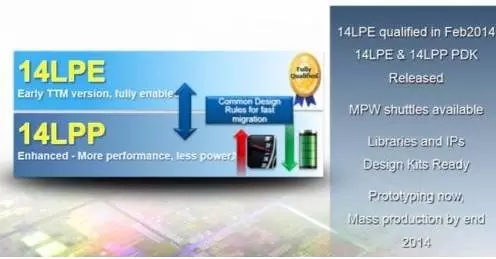

你要说转折点在哪里发生,就是在我们当下14nm工艺节点上,而因为Intel自身在14nm上遇到的技术问题,原本计划的Fab 14工厂升级工艺也被取消了,所以在这个时期我们熟悉Tick-Tock的工艺战略上出现了长时间的停摆,而此前小狮子也跟大家聊过关于年底10nm泡汤,14nm将再续一年的相关故事。而8th的酷睿系列产品也将会使Intel第四代的14nm技术了。

而大佬生气的真正原因,其实一个很重要的原因就是台积电和三星半导体实际在制程工艺方面玩了一个很骚的小花招:半导体实际的复杂程度不言而喻,而大家听到最多的就是XX nm的工艺,其实这个名词代表的是线宽,而理论上来讲,线宽越小,半导体就越小,晶体管也越小,制造工艺越先进。这本身是没有问题的。

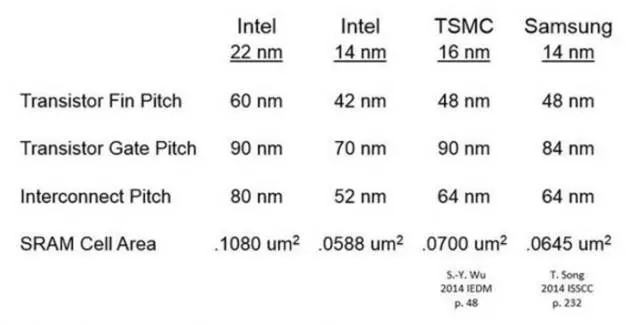

我但是君今天又要出场了

但是!如果去用线宽去整合定义一款半导体工艺的先进程度气势上是并不准确的,因为更细节的栅极距(gate pitch)、鳍片间距(Fin Pitc)这些关键的决定性因素。,Intel早前就对比过他们与TSMC、三星的16、14nm工艺,大家可以在下图有一个较为明显的对比了。

Intel的14nm工艺在这些关键指标上可是要比台积电和三星半导体要好的多,所以从技术的层面来讲,这两家在工艺水平上还是会落后Intel差不多半代的水平。

但是他们俩聪明就聪明在,通过关于半导体工艺的命名对老大哥Intel方面有一个全面的胜利。但是要是一涉及到商业宣传,那就是碾压式的表现了;因为绝大多数消费者都是不会这样锱铢必较的。而对于这个问题实际上业界有有过一些争议,但是苦于没有什么强势性的规定和约束,也就一直处在任其为之的状态。

大佬“报复”方式都不太一样

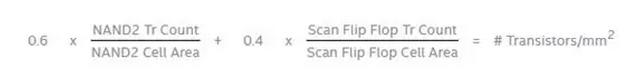

忍受这样的情况没多久,Intel方面就发布了一篇关于清理Intel工艺混乱命名的相关文章,作者是Mark Bohr,他是一名Intel高级院士,也是处理器架构与集成部门的主管,当然是业界资深的一位专家了。而他这篇文章就批判了目前业界在半导体工艺命名上的混乱之态。机智的高级院士还给出了一个更合理的衡量半导体工艺水平的公式:

虽然这个公式较为复杂,过来还是简单来说一下,这个公式分为两部分,一部分计算2bit NAND(4个晶体管)的密度,另一部分则更为复杂,是用来计算的是SFF(scan flip flop)的晶体管密度,0.6和0.4两个数字是这两部分的加权系数。Bohr指出衡量半导体工艺真正需要的是晶体管密度而不是靠嘴炮!

与此同时,Bohr则希望半导体厂商在关于自家工艺节点介绍的时候也应该公布逻辑芯片的晶体管密度,还需要公布一个非常重要的参数,它就是SRAM cell单元面积;因为考虑到每个厂家的工艺不同,所以在NAND+SFF密度之外最好还要独立公布SRAM面积。

但是小狮子个人倒是不觉得尝到了甜头的这两家半导体公司会做出什么相关的改变,因为经过宣传很多朋友都认为台积电和三星半导体在工艺方面对Intel进行了超越,包括三星代工的骁龙835 采用10nm LPE工艺和台积电目前将会开始试产的7nm工艺。而且Intel的新方法有点复杂,对公众来说更不容易理解。不过管他那么多呢?大家理解就好了嘛!

说在最后

虽然批评了这两家公司在命名方面玩的小花招,但是小狮子必须要承认实际上台积电和三星半导体在整体的半导体工艺进展上确实取得了巨大的进步,相比之前一代的落后到现在的“领先”。相信能在未来的个位数工艺节点有着更好、形成超越形式的表现吧。

Intel:我认为我们的10nm需要突然成熟了!

报纸客服电话:4006677866 报纸客服信箱:pcw-advice@vip.sina.com 友情链接与合作:987349267(QQ) 广告与活动:675009(QQ) 网站联系信箱:cpcw@cpcwi.com

Copyright © 2006-2011 电脑报官方网站 版权所有 渝ICP备10009040号